描述

Aldec ALINT-PRO是用VHDL,Verilog和SystemVerilog编写的RTL代码的设计验证解决方案,其重点是确认编码风格和命名契约,合成后的RTL和仿真不匹配,平滑和优化的合成,正确的FSM描述,避免后期设计中的问题,时钟树问题和重新打开,CDC,RDC,DFT,以及可转移性和重用的编码。 在RTL仿真阶段和逻辑综合之前实施ALINT-PRO可防止设计问题向下游扩散,并减少完成设计所需的迭代次数。

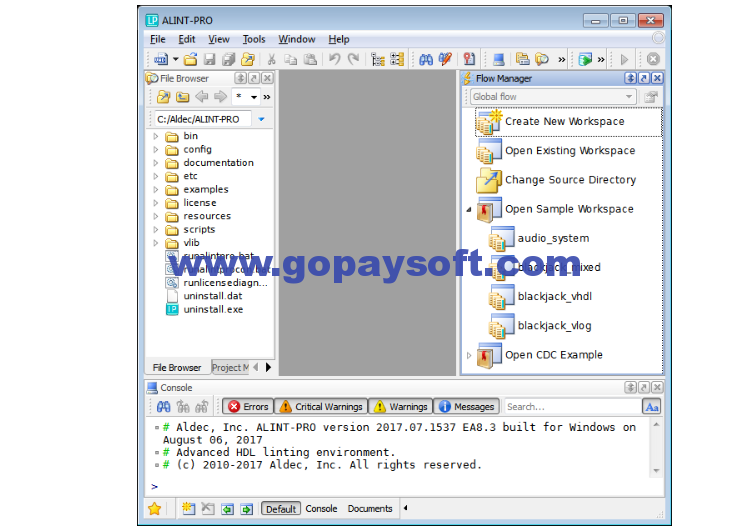

ALINT-PRO具有精心设计的直观框架,可提供高效设计分析的功能,包括RTL原理图,FSM视图,时钟视图和复位,控制原理图,解剖视图,侵权视图,以及专用工具,如CDC视图,RDC视图和CDC原理图,用于分析时钟和复位域的交集。 ALINT-PRO支持2种不同的分层方法:全芯片表面分层和单元分层。这两种方法相辅相成,通常在设计周期的不同阶段应用。

Aldec ALINT-PRO的特性和特点

- 时钟和复位网络分析

- 避免 RTL 后和综合后的仿真错误

- 验证 FSM 描述的准确性

- 提取的 FSM 和指定的 FSM 问题的图形审查

- 代码的可转移性和重用

- 通过ALDEC_CDC插件进行广泛的CDC和RDC控制

- CDC 和 RDC 高级故障排除环境

- 示意图

- DFT评论

- SDCTM 支持

- IP 描述的扩展设计限制

- 批处理和后台执行模式

系统要求

- 视窗® 10/8.1/8/7(64 位)

图片

链接:https://pan.baidu.com/s/1lwElr9-Y_9rhom5HHwJecg

提取码:xeh7

密码文件(S):密码:www.gopaysoft.com

需赞助邀请码获得